CI1301 CI1302 CI1303高性能神经网络智能语音识别芯片 BNPU

芯片概述CI1301、CI1302和CI1303是启英泰伦研发的新一代高性能神经网络智能语音识别芯片,集成了启英泰伦自研的脑神经网络处理器BNPU V3和CPU

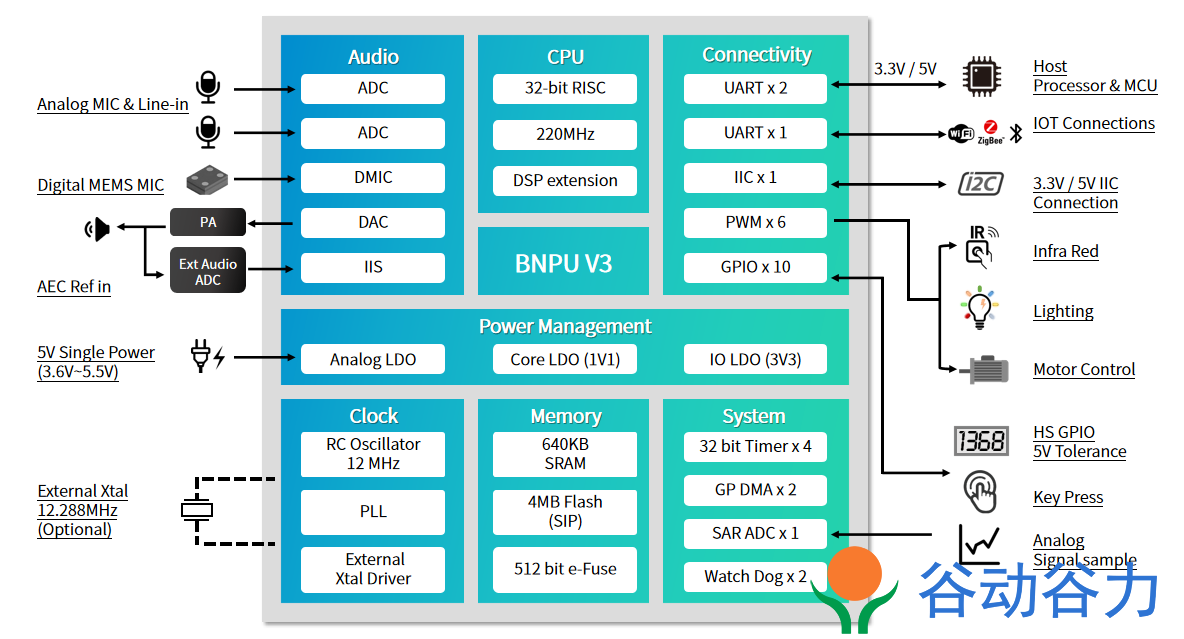

CI1301、CI1302和CI1303是启英泰伦研发的新一代高性能神经网络智能语音识别芯片,集成了启英泰伦自研的脑神经网络处理器BNPU V3和CPU内核,系统主频可达220MHz,内置高达640KByte的SRAM,集成PMU电源管理单元和RC振荡器,集成双通道高性能低功耗Audio Codec和多路UART、IIC、IIS、PWM、GPIO、PDM等外围控制接口。芯片仅需少量电阻电容等外围器件就可以实现各类智能语音产品硬件方案,性价比极高。

CI1301、CI1302和CI1303使用工业级设计标准,具有较高的环境可靠性,芯片工作温度范围在-40°C到 +85°C之间,符合MSL3级湿敏等级,符合IEC 61000-4-2 的4K接触放电试验标准,符合FCC电磁兼容标准,符合ROHS和REACH环保标准。

CI1301、CI1302和CI1303采用了启英泰伦的3代BNPU技术,该技术支持DNN\TDNN\RNN\CNN等神经网络及并行矢量运算,可实现语音识别、声纹识别、命令词自学习、语音检测及深度学习降噪等功能,具备强劲的回声消除和环境噪声抑制能力。该芯片方案还支持汉语、英语、日语等多种全球语言,可广泛应用于家电、照明、玩具、可穿戴设备、工业、汽车等产品领域,实现语音交互及控制和各类智能语音方案应用。

请点击 ☞CI1301芯片数据手册 ☞CI1302芯片数据手册 和 ☞CI1303芯片数据手册 下载完整的芯片数据手册。

表G-1 芯片信息

芯片型号 FLASH容量 RAM容量 封装信息

CI1301 1MByte 640KByte SSOP24(8.6mm*6.0mm*1.64mm)

CI1302 2MByte 640KByte SSOP24(8.6mm*6.0mm*1.64mm)

CI1303 4MByte 640KByte SSOP24(8.6mm*6.0mm*1.64mm)

CI1306 4MByte 640KByte QFN40

注意:CI1303芯片内置Flash容量更大,可以支持更大容量的神经网络模型和更多播报音等功能,具备更好的降噪效果并支持OTA升级功能,CI1301和CI1302芯片暂不支持OTA升级功能,且因Flash容量的原因如支持声纹识别,则不支持语音识别,如想既支持声纹识别又支持语音识别,请用CI1303芯片。

CI1301

CI1301 CI1302

CI1302 CI1303

CI1303

CI1301、CI1302和CI1303可应用的部分产品领域:

智能家电

智能玩具

智能照明

智能可穿戴

智能工业

智能汽车

CI1303应用框图

图G-1 CI1303芯片应用框图

芯片特性如下:

神经网络处理器BNPU V3

采用3代硬件BNPU技术,支持DNN\TDNN\RNN\CNN等神经网络及并行矢量运算,可实现语音识别、声纹识别、命令词自学习、语音检测及深度学习降噪等功能

CPU

32位高性能CPU,运行频率最高支持220MHz

32-bit单周期乘法器,支持DSP扩展加速

存储器

内置640KB SRAM

内置512bit eFuse

内置1-4MB Flash

音频接口

内置高性能低功耗Audio Codec模块,支持双路ADC采样和单路DAC播放

支持Automatic Level Control (ALC)功能

支持8kHz/16kHz/24kHz/32kHz/44.1kHz/48kHz采样率

支持一路IIS音频扩展通路

支持一路PDM接口,可对接单个或两个数字MEMS麦克风

电源管理单元PMU

内置3个高性能LDO,无需外加电源芯片,外围仅需少量阻容器件

支持5V供电直接输入,供电范围最小支持3.6V输入,最大支持5.5V输入

时钟

内置RC振荡器,也支持外接晶体振荡器;开发者可根据不同应用方案选择采用内置RC或者外接晶体作为芯片时钟源

SAR ADC

1路12bit SAR ADC输入通道,采样频率可达1MHz

ADC IO可与数字GPIO进行功能复用

外设和定时器

3路UART接口,最高可支持3M波特率

1路IIC接口,可以外接IIC器件进行扩展

6路PWM接口,灯控和电机类应用可直接驱动

内置4组32-bit timer

内置1组独立看门狗(IWDG)

内置1组窗口看门狗(WWDG)

GPIO

支持10个GPIO口,可以作为主控IC使用

每个GPIO口可配置中断功能,全部GPIO口支持上下拉可配置

部分GPIO支持宽压5V电平信号直接通信,无需外接电平转换但需要外接上拉到5V的电阻

软件开发支持

提供完整软件开发包、应用方案示例和语音开发平台在线制作固件等功能,详情请访问:https://aiplatform.chipintelli.com

固件烧录和保护

支持UART升级和固件保护

EMC和ESD

良好EMC设计,支持FCC标准

内部ESD增强设计,可通过4KV接触放电试验

ROHS和REACH

采用环保材料,支持通过ROHS和REACH测试

封装和工作温度范围

封装形式:SSOP24,尺寸为长8.6mm,宽6mm,高1.64mm

工作环境温度:-40℃ 到85℃

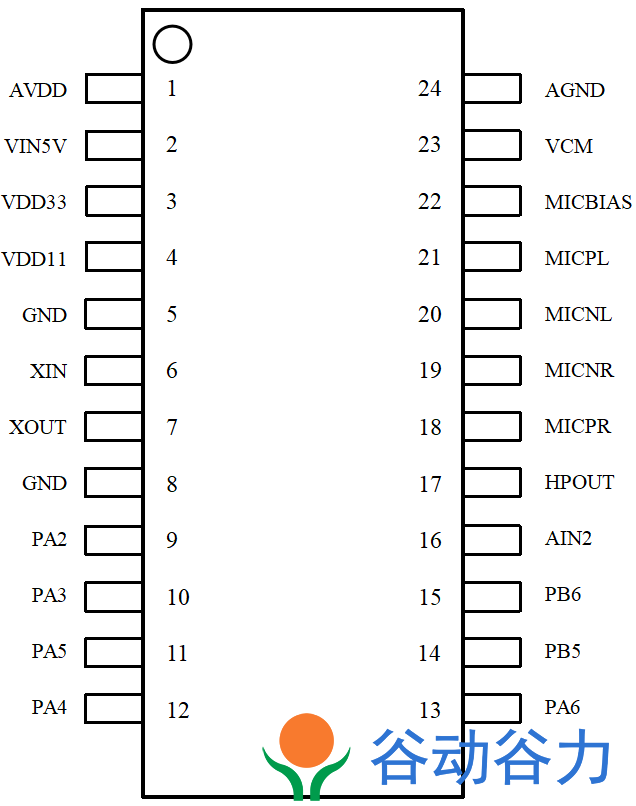

引脚描述

CI1301、CI1302和CI1303芯片引脚完全兼容,引脚图如图P-1所示:

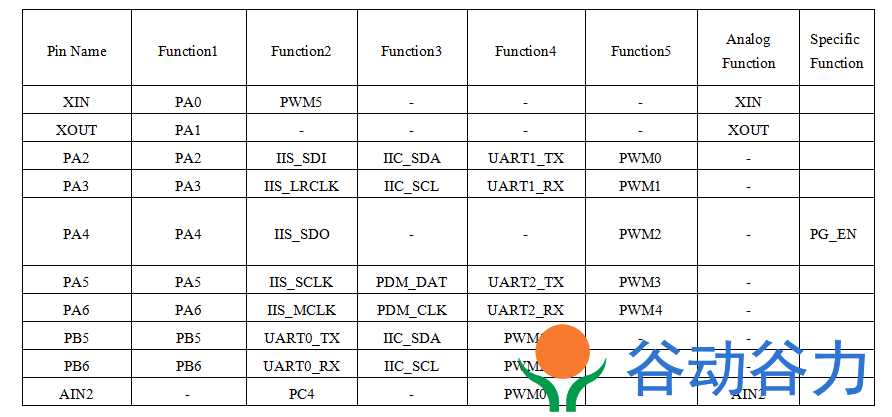

图P-1 芯片引脚图芯片各个引脚功能如下表描述:表P-1 芯片引脚功能描述

上表中 IO引脚的状态定义如下:I 输入O 输出IO 双向P 电源或地T+D 三态正下拉T+U 三态正上拉OUT 上电默认为输出模式IN 上电默认为输入模式所有IO支持驱动能力可配,上下拉电阻可配。Note1:PA4(PG_EN)引脚根据上电时电平状态判断是否进行编程,高电平时启动编程功能。

GPIO

功能介绍

通用I/O 接口支持超多个可编程的输入/输出管脚,每个GPIO端口都有相应的控制寄存器和配置寄存器,以满足不同应用的要求,共分为4组,每组最多可控制8个。其中,GPIO0对应的是芯片的PA口,GPIO1对应的是PB口,GPIO2对应的是PC口,GPIO3对应的是PD口。

GPIO是作为第三功能与其他功能复用,复用关系由寄存器IO_REUSE_CFG配置,该寄存器的具体说明请查看DPMU模块里面的对应内容 ☞请点击这里查看。

复用关系由系统控制单元的寄存器IO_REUSE_CFG配置。。每一组管脚功能使用时需要配置对应的IO_REUSE_CFG寄存器位。模拟管脚需要根据复用情况先选择该管脚是作为模拟管脚使用,还是数字管脚使用。具体复用关系如下图所示:

图GPIO-1 CI1302&CI1303 GPIO复用关系

功能介绍

系芯片有三路UART:UART0 - UART2。UART模块的主要特征如下:

通用定时器和PWM输出

功能介绍通用定时器可产生PWM波输出以及定时器中断信号,两个定时器单元可独立作为单独的定时器工作也可以组合成一个级联的定时器。定时器单元进行32位定时器的递减计数,可产生周期性的中断或者PWM波形,两个定时器单元进行级联工作时,需将TIMER_UNIT_0的周期性的中断作为TIMER_UNIT_1的计数时钟。定时器单元从寄存器TIMER_SC递减TIMER_SPWMC时,PWM输出置高,递减到0时PWM输出置低,同时产生可配宽度的中断信号,每个定时器单元具有如下一些特征:

芯片有四个专用TIMER(TIMER0到TIMER3),六个专用PWM(PWM0到PWM5)。

通用定时器和PWM输出

功能介绍通用定时器可产生PWM波输出以及定时器中断信号,两个定时器单元可独立作为单独的定时器工作也可以组合成一个级联的定时器。定时器单元进行32位定时器的递减计数,可产生周期性的中断或者PWM波形,两个定时器单元进行级联工作时,需将TIMER_UNIT_0的周期性的中断作为TIMER_UNIT_1的计数时钟。定时器单元从寄存器TIMER_SC递减TIMER_SPWMC时,PWM输出置高,递减到0时PWM输出置低,同时产生可配宽度的中断信号,每个定时器单元具有如下一些特征:

芯片有四个专用TIMER(TIMER0到TIMER3),六个专用PWM(PWM0到PWM5)。

IIS

功能介绍芯片内置多路IIS,外部可使用的为IIS0,该接口可以用来对接外部16/24/32位立体声数字音频信号编解码电路,可用于芯片内部CODEC无法满足应用需求的场合。

IIS传输有专用的DMA通道,此处不进行详细描述,芯片配套SDK开发包中已有完整的功能示例和驱动代码,用户可直接调用。

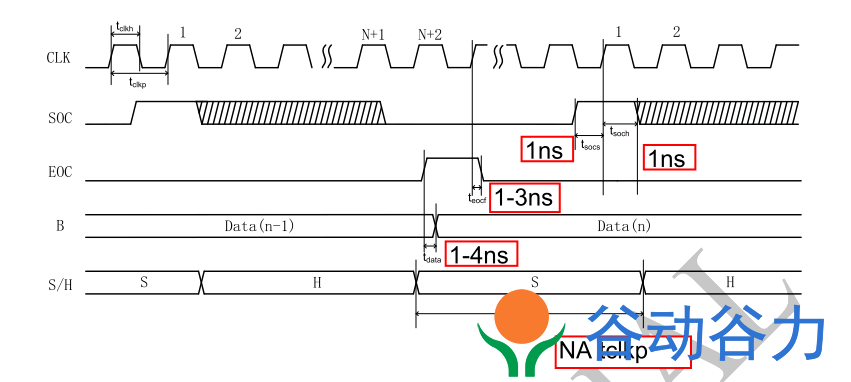

功能介绍芯片集成了一个12位的ADC,其主要特点如下:

ADC分辨率为12-bit;

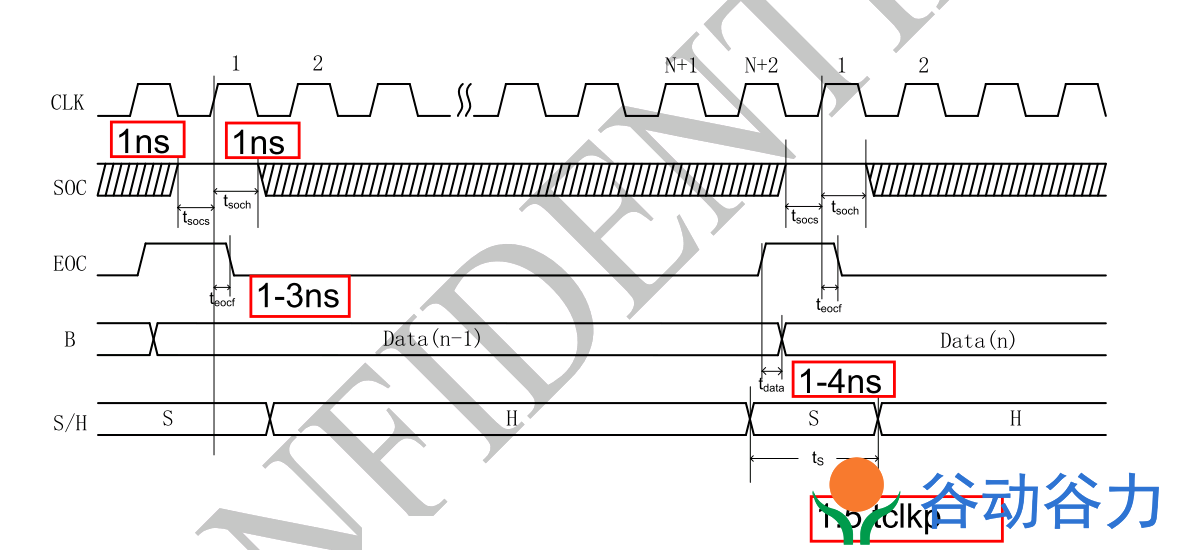

图A-1 ADC单次采样模式时序图

图A-2 ADC连续采样模式时序图

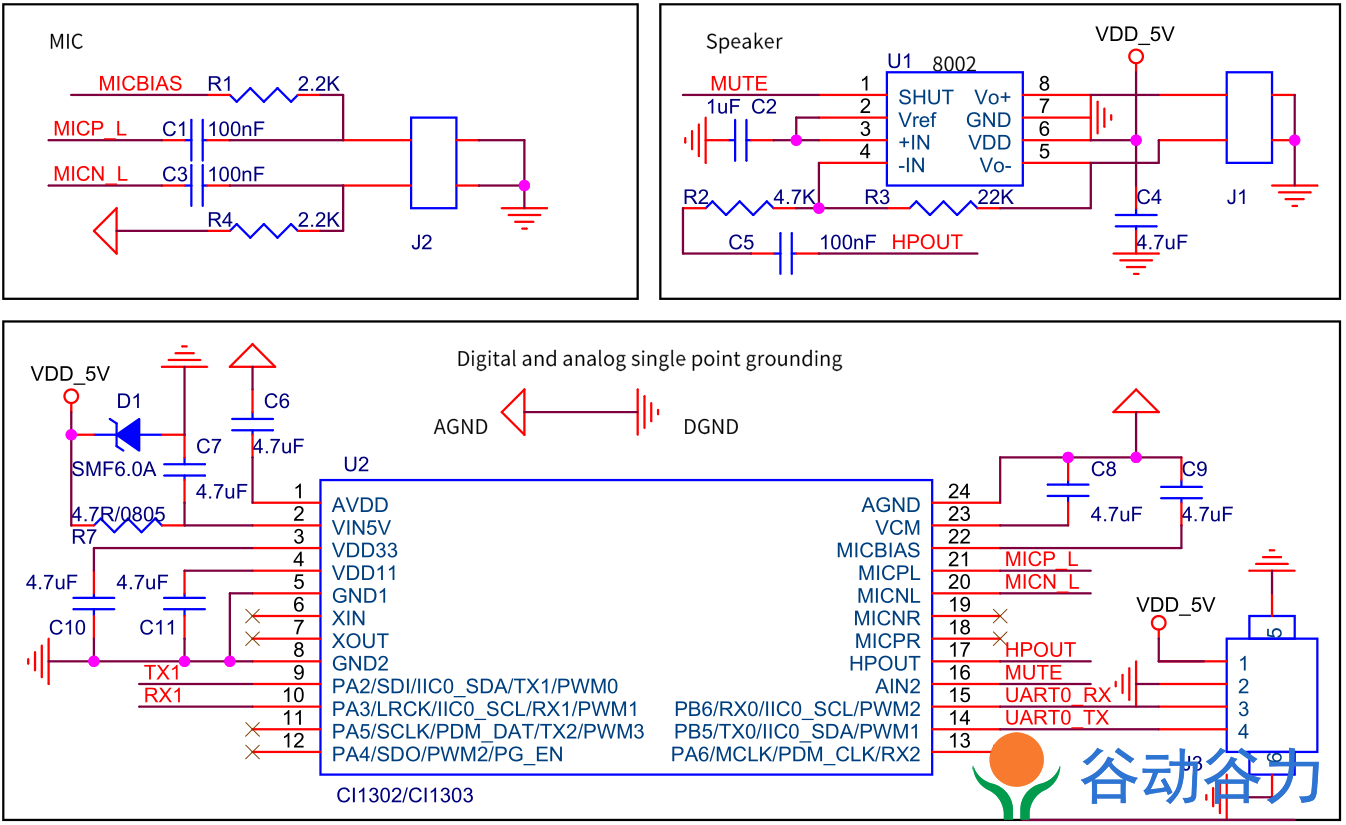

硬件设计CI1301、CI1302和CI1303芯片外围仅需要少量器件就可以支持各类语音应用。针对语音部分,该芯片可以支持单麦克风差分输入或单麦克风单端输入,也可以选择是否需要AEC回声消除功能。用户可以根据设计的应用方案功能、功耗和成本要求选择合适的电路,下面对该芯片一个最简单的应用参考电路图做具体描述。

应用参考电路图

应用参考电路图如图H-1,以CI1303为例(CI1301、CI1302和CI1303的引脚及电路图连接方式完全相同)。

图H-1 最简方案的应用参考电路图上图为CI1303一个支持单麦克风差分输入和功放输出的最简应用方案电路图。该芯片可以采用5V直接供电,用户可按照上图中对应的外围器件规格来进行设计。

原理图设计时如果要考虑板级在线升级功能,可以将UART0引脚引出,以方便PCB板贴片完成后通过UART0对主芯片内部的Flash进行固件升级。芯片的PA4(PG_EN)引脚内部带上拉,上电默认为升级模式,开机后要检测外部UART0口发来的升级信号,如果有则直接启动升级。芯片默认的开机时间因为增加了升级模式的检测而延长,大概约850mS;如果用户对开机时间有很高的要求,可以将PA4脚引出,增加两个2.2KΩ的下拉电阻到地,两个2.2KΩ电阻连接的中间增加一个测试点,此时芯片开机为正常模式,开机时间大概约350mS,可以缩短开机时间。如果此时要在线升级可以通过外部给两个2.2KΩ电阻连接的中间测试点供高电平,将PA4引脚拉高,再通过UART0升级。

该芯片方案可选用差分麦克风设计或单端麦克风设计,推荐采用上图中的差分麦克风设计。如果用户对成本有要求,可以将上图中麦克风部分修改为单端麦克风设计,可以比差分麦克风少使用一些被动器件,但该方式仅推荐应用在麦克风线长小于20厘米的场合中,否则会因为线太长,抗干扰效果不够,导致语音识别效果没有差分麦克风设计的方式好。上图中功放采用的是AB类的功放,推荐采用8002功放芯片,用户也可以按照方案的要求自行选择功放芯片,如果不需要功放功能时也可以去掉该部分电路以降低成本。用户如果有AEC回声消除功能的需求,可以利用一个麦克风输入通道来接AEC的模拟信号输入。

用户如果对方案的功耗没有特殊要求时,建议直接采用芯片内部的PMU供电,如果有功耗要求,可以采用增加外部DCDC芯片给芯片1.1V供电,以降低功耗。芯片的UART口均支持5V通信,上图中的UART0口是接的3.3V信号,如果要接5V,在UART0的RX和TX管脚外围增加连接到5V的上拉电阻即可,不用额外增加电压转换电路。

启英泰伦提供了多种方案参考原理图,可以满足大多数通常应用场景。客户在实际应用开发中需要根据具体产品功能性能要求,系统特性及应用场景等审慎选择参考其中一种最适合产品的参考原理图进行参考和设计优化。 由于启英泰伦无法掌握所有产品系统和应用知识,望客户或方案合作方在量产前结合产品系统和应用场景对产品功能性能(含语音芯片及模块与产品系统的匹配性)进行充分的测试验证。如果在设计修改过程中有不清楚不确定的问题点,请联系启英泰伦FAE工程师进行充分沟通。